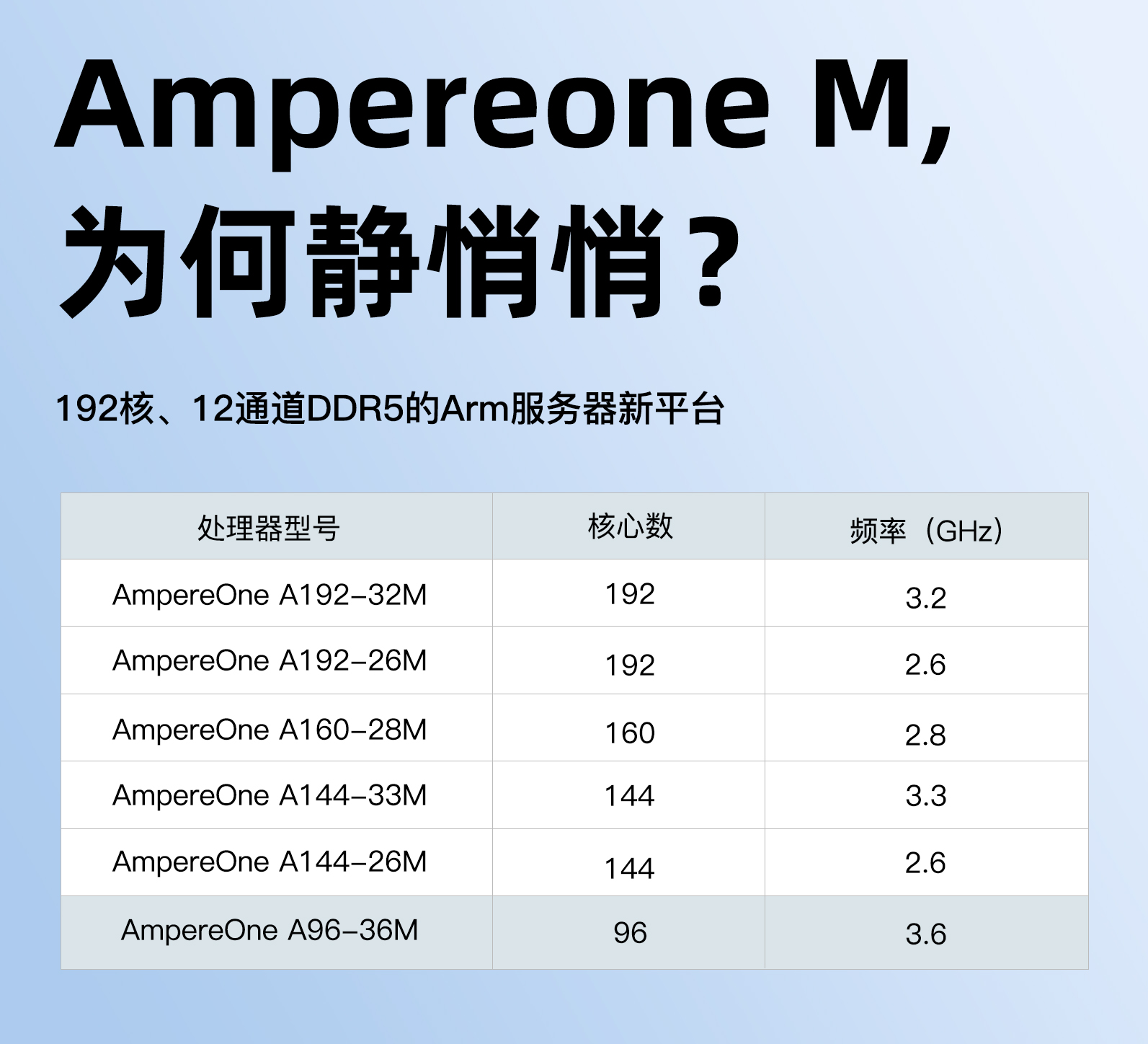

AmpereOne M为何缺乏市场声量?――192核、12通道DDR5的服务器新平台

Ampere Computing 正在推动自研 Arm 服务器芯片向更高带宽、更大内存容量的方向迈进。新推出的 AmpereOne M,在原有 AmpereOne 架构基础上,扩展至 12 通道 DDR5 内存,核心数最高达 192 个,同时保留了 96 条 PCIe 5.0 通道。

这款芯片采用了先进的制程工艺,确保了更高的性能和能效比,其强大的计算能力能够满足大规模数据处理和高性能计算的需求。发布虽有所延迟,但其设计理念和技术演进依然清晰可见,背后显露出 Ampere 面向未来数据中心的战略野心,旨在提供更高效、更灵活的计算解决方案。

AmpereOne M 的架构调整不仅提升了内存带宽和存储容量,还优化了数据传输速度,使其在处理复杂任务时表现出色。这些改进为 Ampere 在企业 ARM 服务器市场上的竞争提供了新的契机,进一步巩固了其在高性能计算领域的地位。 AmpereOne M的推出,让人们更加期待Arm架构在高性能服务器市场的应用。这款新平台的最大特点是内存通道数的扩展,从8通道提升至12通道DDR5-5600,结合最高192核心的设计,充分释放了并行计算与内存带宽的潜力。每个核心配备80KB L1和2MB L2缓存,系统级缓存总计64MB,Ampere针对高并发、数据密集型任务进行了优化。

AmpereOne M的推出,让人们更加期待Arm架构在高性能服务器市场的应用。这款新平台的最大特点是内存通道数的扩展,从8通道提升至12通道DDR5-5600,结合最高192核心的设计,充分释放了并行计算与内存带宽的潜力。每个核心配备80KB L1和2MB L2缓存,系统级缓存总计64MB,Ampere针对高并发、数据密集型任务进行了优化。

虽然DDR5-5600的单条速率不及Intel Xeon P核平台上的DDR5-6400,但12通道布局带来的并行带宽仍能满足大量线程的内存访问需求,尤其在1 DPC的限制下,内存访问延迟更易于预测和优化。

AmpereOne M支持96条PCIe Gen5通道,可连接24个设备,强调I/O灵活性,适合存储密集型部署和边缘计算扩展NVMe SSD,但暂不支持x2分叉的主动-主动NVMe组网。它采用台积电5nm制程,下一代AmpereOne MX预计将升级至256核心和3nm制程,提升核心规模和能效。M系列的升级主要在结构性方面,增强内存与I/O模块,提高负载能力和可扩展性,而非架构重构。架构上延续自研Arm v8.6+ ISA核心理念,不依赖Arm公版Neoverse内核,与NVIDIA Grace系列形成显著差异,赋予Ampere更强的核心设计、能耗控制和调度主控权。 AmpereOne M配置提升明显,市场存在感却极低。原本计划2024年第四季度上市,Ampere Computing却未发正式公告,于2025年第二季度通过X平台低调上线。产品页面信息有限,客户案例、部署场景和合作伙伴均未披露。

AmpereOne M配置提升明显,市场存在感却极低。原本计划2024年第四季度上市,Ampere Computing却未发正式公告,于2025年第二季度通过X平台低调上线。产品页面信息有限,客户案例、部署场景和合作伙伴均未披露。

该产品自去年底起已向部分客户发货,封闭式推广在芯片行业罕见,尤其是在AMD EPYC Turin和Intel Xeon Clearwater Forest的竞争下,Ampere的“按兵不动”令人不解。软银拟收购Ampere是否影响市场策略尚不明确,但市场的静默形成了一种“平台强,市场无声”的反差。

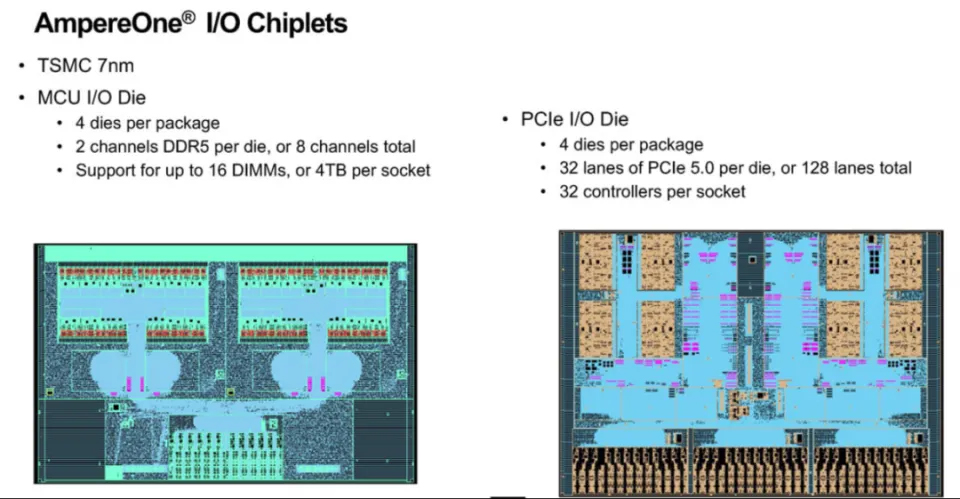

Ampere过去的主要合作伙伴Oracle在两年前就展示了Ampere平台的主板,AmpereOne M的大插槽设计也在2023年Computex展会上亮相。显然,这不是一个仓促上线的平台。从路线图看,AmpereOne M属于既定规划。其插槽结构依旧为LGA5964,核心计算与缓存模块周围环绕I/O和内存控制器模块。这种chiplet组合方式提升了芯片制造灵活性,也为后续扩展预留空间。

通过集成更多内存控制模块,Ampere实现从8通道到12通道的扩展,完成M系列的定位,与Intel的EMIB扩展CXL memory策略相似。尽管AmpereOne M暂不支持DDR5-6400,但其发布时间晚于2024年主流新品,市场定位仍有参考价值。

同期推出的Sierra Forest采用8通道DDR5-6400,EPYC Turin支持12通道。Ampere选择DDR5-5600是基于平台功耗、成本与稳定性的考虑,与A192-32M型号相比,其在3.2GHz频率下的TDP为348W,功耗控制良好。