DRAM,30年技术博弈的新篇章

在科技飞速发展的当下,DRAM制程技术的进步一直是行业关注的焦点。如何跨越10nm的门槛,曾是整个行业共同面临的难题。然而,SK海力士为我们带来了突破性的答案。在2025年于日本东京举行的IEEE VLSI研讨会中,SK海力士展示了未来30年的新DRAM技术路线图,为整个行业指明了方向。

SK海力士的技术专家们提出,4F2 VG和3D DRAM技术将应用于10nm及以下级别的内存。这一消息无疑给行业内带来了巨大的震动。那么,究竟是什么原因使得10nm的DRAM技术如此难以攻克?在未来的30年中,DRAM市场为何如此依赖3D技术?而4F2 VG技术又有哪些独特之处?让我们一一进行探讨。

首先,业内普遍将上一代DRAM芯片按照1X、1Y、1Z的工艺进行区分,其中1Xnm工艺相当于16-19nm制程工艺,1Ynm相当于14-16nm制程工艺,而1Znm则相当于12-14nm制程工艺。相对地,新一代的1a、1b和1c则分别代表14-12nm、12-10nm以及10nm及以下的制程工艺。10nm的制程技术被视为DRAM发展道路上的绊脚石,主要是因为随着工艺的微缩,电路图案的精密度已经接近物理定律的极限。在晶圆上定义这些微小的电路图案时,面临着工艺完整性、成本控制、单元泄漏、电容管理、刷新技术以及传感裕度等多方面的严峻挑战。

法国著名分析机构Yole指出,即便借助先进的EUV光刻技术,平面缩放技术也无法在整个下一个十年中满足所需的位密度提升需求。这意味着传统的二维平面缩放技术即将走到尽头。因此,1c DRAM及之后的技术发展虽困难重重,但已被存储行业的三大巨头所重视。

回溯至去年8月,SK海力士便已宣布成功完成了第六代10nm级(1c)工艺的DRAM开发。这一成就的背后,是SK海力士对技术难点的深刻认知与不懈攻克。值得注意的是,早在2021年,SK海力士便已率先在其10nm级第四代DRAM中应用了EUV光刻技术,展现出其在技术革新上的前瞻性与领导力。

而美光科技也在今年2月宣布,已向生态系统合作伙伴及特定客户提供了专为下一代CPU设计的1γ(1-gamma)第六代(10纳米级)DRAM节点的DDR5内存样品,进一步推动了10nm级DRAM技术的商业化进程。三星虽然在其第六代10纳米级1c DRAM制程开发进度上出现延迟,预计完成时间从2024年年底推迟至2025年6月,但这一延迟也意味着其技术储备将更为成熟,或将带来更为惊艳的技术突破。

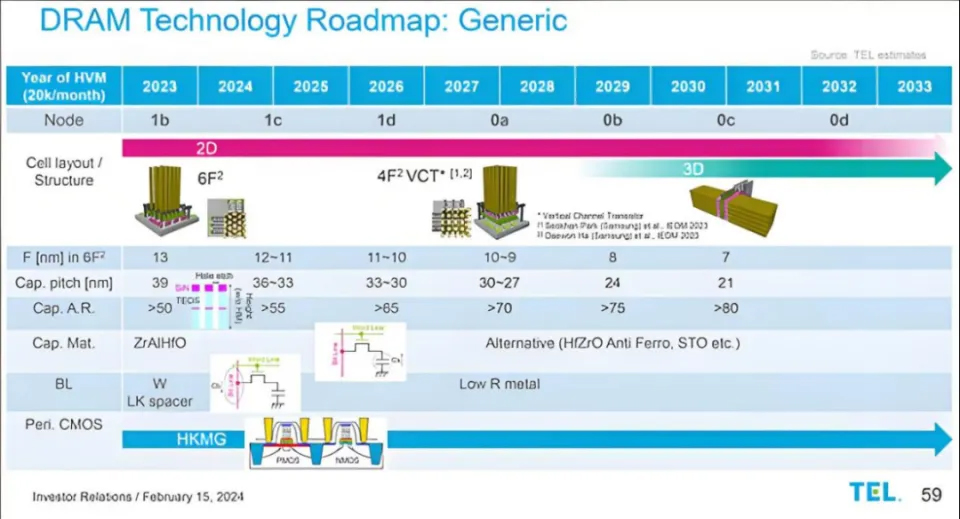

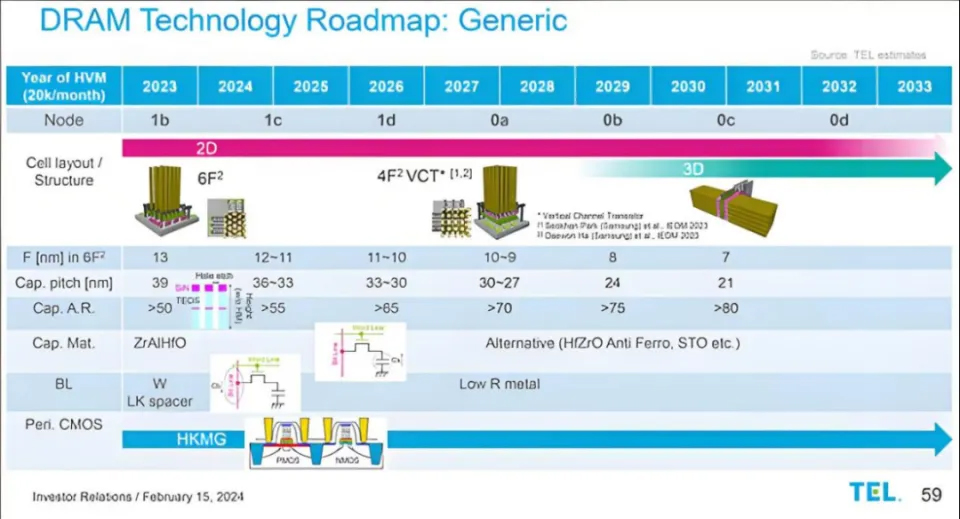

上图显示,10nm以下的工艺节点将命名为0a、0b、0c、0d,其中0a预计在2027年底到2028年初量产,0d则将在2032年出现。到2030年,DRAM市场将高度依赖3D技术。

4F2 VG DRAM技术灵感来源于NAND闪存,采用混合键合和垂直堆叠晶体管,即3D DRAM。三星称之为“垂直通道晶体管”(VCT)。4F²结构自下而上分别为源极、闸极、汲极和电容器。字元线连接闸极,位元线连接源极。通过将平面栅极结构调整为垂直方向,4F2 VG减少了单一数据存储单元的面积,实现了高集成度、高速度和低功耗。

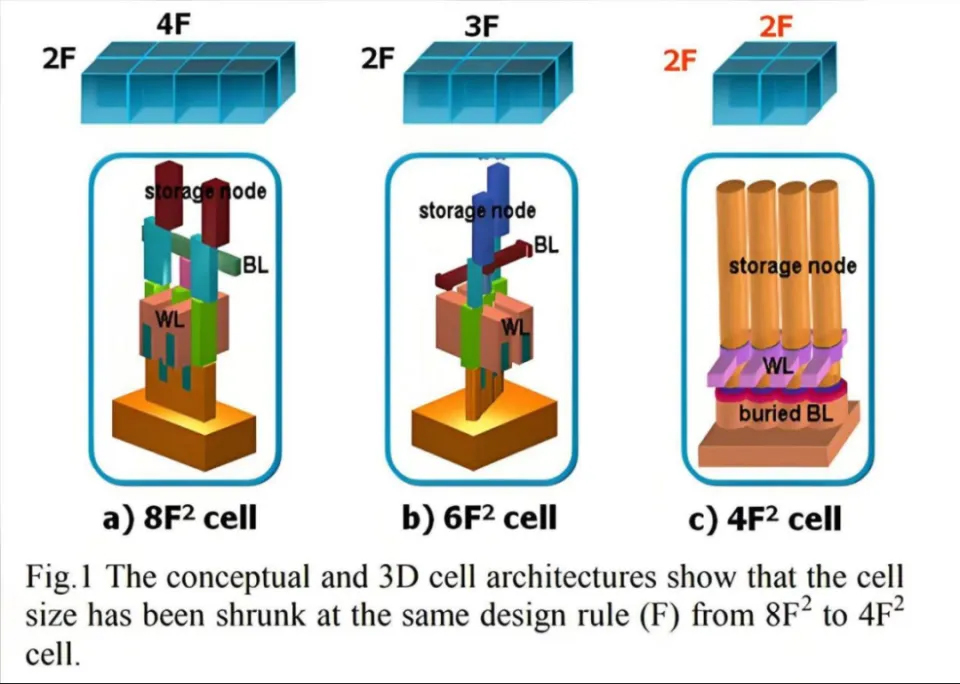

6F²:自130纳米及以下制程,6F² BCAT结构登场,位线3格、字线2格,提升密度。然而,线路宽度缩小至10纳米级,电流泄漏、信号干扰频发,平面排列难以为继。

4F²:为高效利用面积,单元阵列改为垂直堆叠。4F²结构源极、栅极、漏极垂直排列,源极接位线,栅极连字线,漏极堆叠电容器,面积缩小约30%。该结构研发已久,但制造难度高。

三星也在研发4F² DRAM,2023年组建团队推进应用,计划2025年推出样品,但可能仅为内部试制。东京电子预计采用VCT和4F²技术的DRAM将在2027-2028年问世。

三星采用VCT技术将晶体管垂直排列,单元面积缩小30%,并使用HZO材料优化电荷存储性能,已研发128Gb容量3D X-DRAM样品,目标2030年前扩展至1Tb。三星在美国硅谷设立新的研发实验室,专注于新一代DRAM产品开发,计划2025年量产,并在20272028年将制程节点缩小到8nm9nm。

SK海力士在“VLSI 2024”大会上展示了5层堆叠3D DRAM原型,良率达56.1%,并首次披露具体数据和运行特性。研究将IGZO材料应用于3D DRAM,以解决带宽和延迟问题。IGZO材料由铟、镓、氧化锌组成,分为非晶质和晶化两种。

美光自2019年起研究3D DRAM,截至2022年8月已获得30多项专利。2023年末在IEEE IEDM会议上披露了32Gb 3D NVDRAM研发成果,但分析师认为其难以商业化量产。

此外,创业公司如NEO Semiconductor推出的3D X-DRAM技术,单元阵列结构类似3D NAND Flash,采用FBC,可通过添加层掩模形成垂直结构,实现高良率、低成本和显著密度提升。NEO称3D X-DRAM技术可跨230层实现128Gb密度,是当前DRAM密度的8倍。

SK海力士的技术专家们提出,4F2 VG和3D DRAM技术将应用于10nm及以下级别的内存。这一消息无疑给行业内带来了巨大的震动。那么,究竟是什么原因使得10nm的DRAM技术如此难以攻克?在未来的30年中,DRAM市场为何如此依赖3D技术?而4F2 VG技术又有哪些独特之处?让我们一一进行探讨。

首先,业内普遍将上一代DRAM芯片按照1X、1Y、1Z的工艺进行区分,其中1Xnm工艺相当于16-19nm制程工艺,1Ynm相当于14-16nm制程工艺,而1Znm则相当于12-14nm制程工艺。相对地,新一代的1a、1b和1c则分别代表14-12nm、12-10nm以及10nm及以下的制程工艺。10nm的制程技术被视为DRAM发展道路上的绊脚石,主要是因为随着工艺的微缩,电路图案的精密度已经接近物理定律的极限。在晶圆上定义这些微小的电路图案时,面临着工艺完整性、成本控制、单元泄漏、电容管理、刷新技术以及传感裕度等多方面的严峻挑战。

法国著名分析机构Yole指出,即便借助先进的EUV光刻技术,平面缩放技术也无法在整个下一个十年中满足所需的位密度提升需求。这意味着传统的二维平面缩放技术即将走到尽头。因此,1c DRAM及之后的技术发展虽困难重重,但已被存储行业的三大巨头所重视。

回溯至去年8月,SK海力士便已宣布成功完成了第六代10nm级(1c)工艺的DRAM开发。这一成就的背后,是SK海力士对技术难点的深刻认知与不懈攻克。值得注意的是,早在2021年,SK海力士便已率先在其10nm级第四代DRAM中应用了EUV光刻技术,展现出其在技术革新上的前瞻性与领导力。

而美光科技也在今年2月宣布,已向生态系统合作伙伴及特定客户提供了专为下一代CPU设计的1γ(1-gamma)第六代(10纳米级)DRAM节点的DDR5内存样品,进一步推动了10nm级DRAM技术的商业化进程。三星虽然在其第六代10纳米级1c DRAM制程开发进度上出现延迟,预计完成时间从2024年年底推迟至2025年6月,但这一延迟也意味着其技术储备将更为成熟,或将带来更为惊艳的技术突破。

上图显示,10nm以下的工艺节点将命名为0a、0b、0c、0d,其中0a预计在2027年底到2028年初量产,0d则将在2032年出现。到2030年,DRAM市场将高度依赖3D技术。

4F2 VG DRAM技术灵感来源于NAND闪存,采用混合键合和垂直堆叠晶体管,即3D DRAM。三星称之为“垂直通道晶体管”(VCT)。4F²结构自下而上分别为源极、闸极、汲极和电容器。字元线连接闸极,位元线连接源极。通过将平面栅极结构调整为垂直方向,4F2 VG减少了单一数据存储单元的面积,实现了高集成度、高速度和低功耗。

确实存在6F²和8F²等技术变种。

6F²:自130纳米及以下制程,6F² BCAT结构登场,位线3格、字线2格,提升密度。然而,线路宽度缩小至10纳米级,电流泄漏、信号干扰频发,平面排列难以为继。

4F²:为高效利用面积,单元阵列改为垂直堆叠。4F²结构源极、栅极、漏极垂直排列,源极接位线,栅极连字线,漏极堆叠电容器,面积缩小约30%。该结构研发已久,但制造难度高。

三星也在研发4F² DRAM,2023年组建团队推进应用,计划2025年推出样品,但可能仅为内部试制。东京电子预计采用VCT和4F²技术的DRAM将在2027-2028年问世。

三星采用VCT技术将晶体管垂直排列,单元面积缩小30%,并使用HZO材料优化电荷存储性能,已研发128Gb容量3D X-DRAM样品,目标2030年前扩展至1Tb。三星在美国硅谷设立新的研发实验室,专注于新一代DRAM产品开发,计划2025年量产,并在20272028年将制程节点缩小到8nm9nm。

SK海力士在“VLSI 2024”大会上展示了5层堆叠3D DRAM原型,良率达56.1%,并首次披露具体数据和运行特性。研究将IGZO材料应用于3D DRAM,以解决带宽和延迟问题。IGZO材料由铟、镓、氧化锌组成,分为非晶质和晶化两种。

美光自2019年起研究3D DRAM,截至2022年8月已获得30多项专利。2023年末在IEEE IEDM会议上披露了32Gb 3D NVDRAM研发成果,但分析师认为其难以商业化量产。

此外,创业公司如NEO Semiconductor推出的3D X-DRAM技术,单元阵列结构类似3D NAND Flash,采用FBC,可通过添加层掩模形成垂直结构,实现高良率、低成本和显著密度提升。NEO称3D X-DRAM技术可跨230层实现128Gb密度,是当前DRAM密度的8倍。