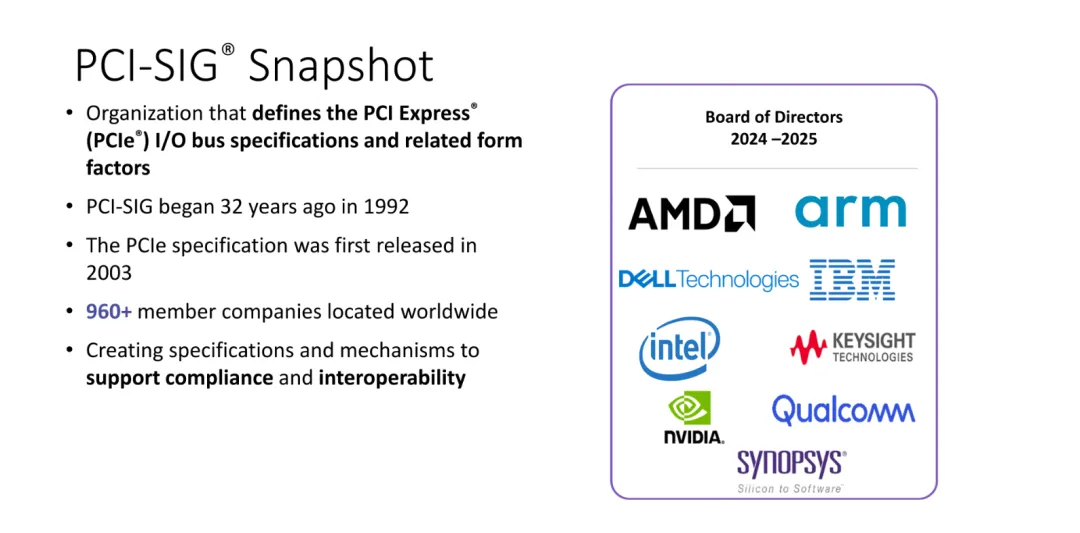

PCIeЃЌПёь20Фъ

дкPCIeММЪѕЕЎЩњжЎЧАЃЌМЦЫуЛњЯЕЭГжївЊвРРЕВЂаазмЯпММЪѕНјааФкВПЪ§ОнДЋЪфЁЃЦфжаЃЌзюОпДњБэадЕФФЊЙ§гкPCIЃЈPeripheral Component InterconnectЃЉзмЯпЁЃетвЛзмЯпММЪѕгЩIntelгк1992ФъЭЦГіЃЌжМдкНтОідчЦкISAКЭVLBзмЯпЕФЫйЖШКЭМцШнадЮЪЬтЁЃPCIзмЯпдЪаэЖрИіЩшБИЙВЯэЪ§ОнТЗОЖЃЌЦфзюДѓДјПэПЩДя133 MB/sЃЌетдкЕБЪБЮовЩЪЧЯрЕБИпаЇЕФЁЃ

ШЛЖјЃЌЫцзХМЦЫуЛњгВМўадФмЕФВЛЖЯЗЩдОЃЌPCIзмЯпЕФОжЯоадвВж№НЅБЉТЖГіРДЁЃВЂааДЋЪфЗНЪНДјРДСЫбЯжиЕФаХКХЫЅМѕЮЪЬтЃЌЭЌЪБЪБжгЭЌВНЕФРЇФбвВШевцЭЙЯдЃЌетаЉЖМЯожЦСЫДЋЪфЫйЖШЕФНјвЛВНЬсЩ§ЁЃе§ЪЧгЩгкетаЉЦПОБЃЌВХДйЪЙСЫЖдаТаЭзмЯпММЪѕЕФЦШЧаашЧѓЃЌPCIeвђДЫгІдЫЖјЩњЁЃ

зїЮЊЯжДњМЦЫуЦНЬЈКЫаФЕФЛЅСЊММЪѕЃЌPCIeЦОНшЦфДЎаазмЯпМмЙЙЃЌЪЕЯжСЫДЋЭГPCIВЂаазмЯпЕФШЋУцИяаТЁЃЯрНЯгкВЂааДЋЪфФЃЪНЃЌPCIeЭЈЙ§вдЯТШ§ДѓКЫаФЬиадДђЦЦСЫДЋЭГММЪѕЕФЪјИПЃК

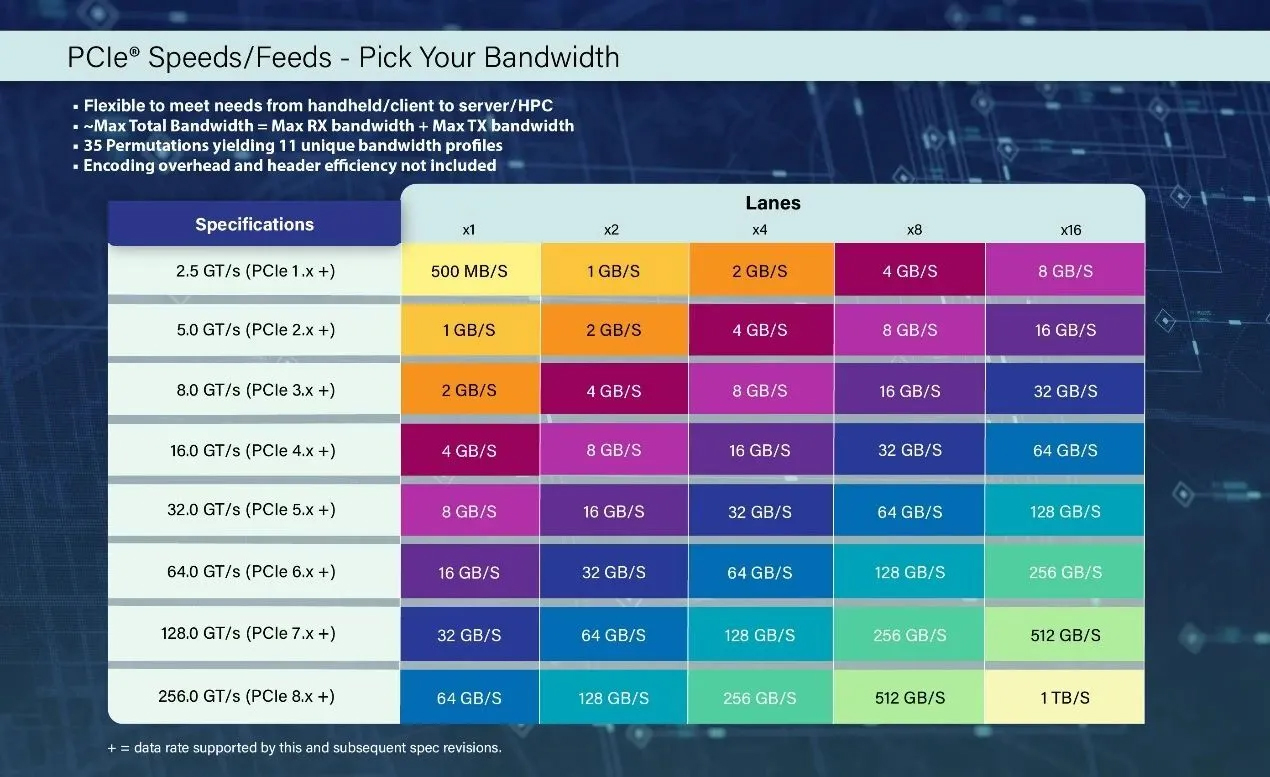

ЪзЯШЃЌВЩгУДЎааЭЈаХЛњжЦЃЌвдДЎааДЋЪфЬцДњДЋЭГЕФВЂааМмЙЙЃЌДгЮяРэВуУцМѕЩйСЫаХКХИЩШХЃЌДгЖјЯджјЬсЩ§СЫЪ§ОнДЋЪфЕФаЇТЪМАгааЇОрРыЁЃЦфДЮЃЌЕуЖдЕуСЌНгЩшМЦЪЙЕУУПИіЭтЩшЭЈЙ§ЖРСЂСДТЗжБНггыИљИДКЯЬхЖдНгЃЌЯћГ§СЫзмЯпОКељЕФЦПОБЃЌЪЕЯжСЫЪ§ОнДЋЪфЕФжБНгадгыИпаЇадЁЃзюКѓЃЌЦфПЩРЉеЙЕФДјПэФмСІЃЌжЇГжЭЈЙ§ЭЈЕРЃЈLaneЃЉЪ§СПЕФЯпадРЉеЙРДСщЛюЦЅХфВЛЭЌЩшБИЕФадФмашЧѓЁЃетаЉММЪѕЬиадВЛНіЮЊЯдПЈЁЂДцДЂЩшБИЁЂЭјПЈЕШЭтЩшЬсЙЉСЫдЖГЌДЋЭГPCIЕФДЋЪфДјПэКЭИќЕЭЕФбгГйЃЌЛЙЭЈЙ§ИпаЇЕФзЪдДЕїЖШНЕЕЭСЫЯЕЭГеМгУЁЃPCIeвбШЛГЩЮЊжЇГХЕБДњМЦЫуЛњгВМўИпЫйЛЅСЊЕФКЫаФММЪѕЛљЪЏЃЌЩюПЬгАЯьзХећИіМЦЫуЯЕЭГЕФМмЙЙЩшМЦгыадФмгХЛЏЗНЯђЁЃ

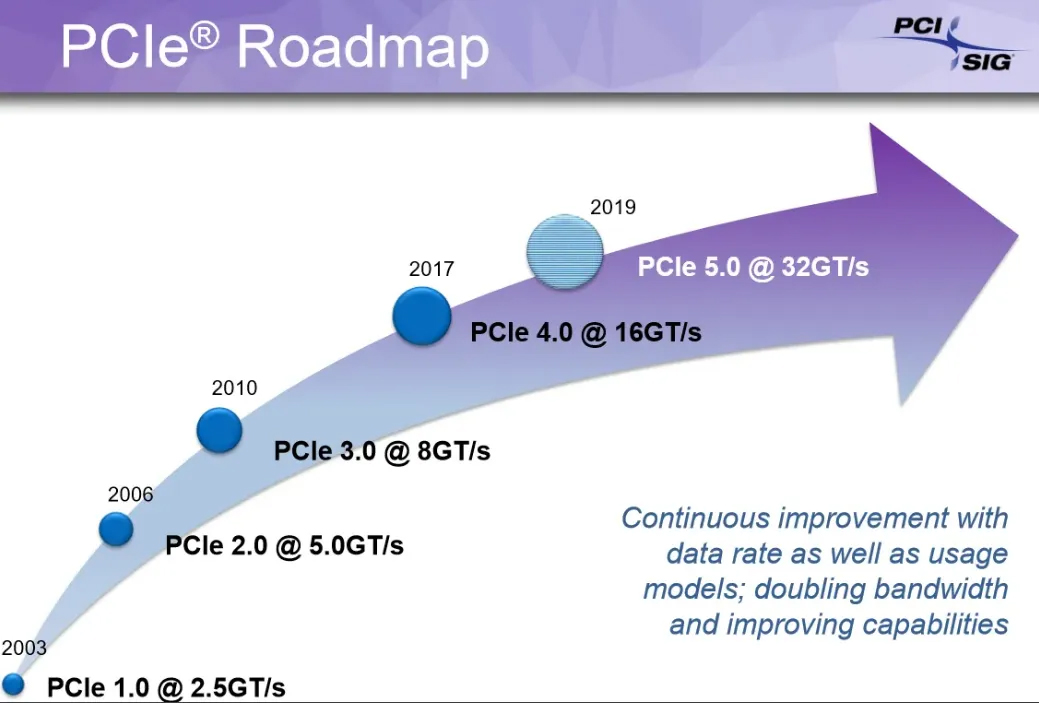

зд2003ФъЪзИіАцБОЕФЮЪЪРЃЌPCIeММЪѕРњОЖрДЮжиДѓЕќДњЃЌДгзюГѕЕФ1.0АцБОж№ВНбнНјжСШчНёЕФ8.0АцБОЁЃдкетТўГЄЕФРњГЬжаЃЌЦфЪ§ОнДЋЪфЫйТЪгыадФмЛёЕУСЫГжајЕФЯджјЬсЩ§ЁЃ

PCIe 1.0ЃКДЎааЛЅСЊЦ№ЕуЃЌ2.5GT/sПЊЦєзмЯпИяУќ

зїЮЊPCI ExpressММЪѕЕФЕьЛљжЎзїЃЌPCIe 1.0гк2003ФъгЩPCI-SIGТЁжиЭЦГіЃЌаћИцСЫМЦЫуМмЙЙДгДЋЭГPCIзмЯпЯђЯШНјДЎааЛЅСЊЪБДњЕФжиДѓПчдНЁЃГѕЪМЕФЕЅЭЈЕРДЋЪфЫйТЪДяЕН2.5GT/sЃЌНшжњ8b/10bБрТыММЪѕЃЌЪЕЯжСЫДѓдМ250MB/sЕФЕЅЭЈЕРДјПэЁЃЯрНЯгкДЫЧАЕФВЂааPCIзмЯпЃЌPCIe 1.0ЦОНшЦфИяУќадЕФЕуЖдЕуДЎааСДТЗЩшМЦЃЌМЋДѓЕиМѕЩйСЫаХКХИЩШХЃЌДгЖјЯджјЬсЩ§СЫЪ§ОнДЋЪфЕФЮШЖЈадКЭећЬхаЇТЪЁЃЦфДјПэЕФЗЩдОдЖдЖГЌЙ§СЫДЋЭГЕФPCIБъзМЃЌзмЯпЫйЖШвВЕУЕНСЫПеЧАЕФЬсЩ§ЁЃ

2005ФъЮЪЪРЕФPCIe 1.1АцБОЃЌдкЮЌГжКЫаФЫйТЪВЛБфЕФЧАЬсЯТЃЌЖдММЪѕЙцЗЖЕФЯИНкНјааСЫШЋУцЕФГЮЧхгыгХЛЏЃЌНјвЛВНЙЎЙЬСЫМцШнадИљЛљЁЃетПюБъзМбИЫйГЩЮЊдчЦкЯдПЈЁЂЭјПЈЕШРЉеЙЩшБИЕФжїСїНгПкбЁдёЃЌЮЊКѓајЕФЕќДњЗЂеЙЦЬЦНСЫЕРТЗЁЃ

PCIe 2.0ЃКЫйТЪЗБЖгыМцШнадбгај

ЫцзХПЦММЕФВЛЖЯНјВНЃЌ2007ФъГѕЃЌPCIe 2.0ЙцЗЖе§ЪНЗЂВМЁЃЯрНЯгкжЎЧАЕФPCIe 1.xАцБОЃЌPCIe 2.0дкДЋЪфадФмЩЯЪЕЯжСЫОоДѓЕФЗЩдОЁЃУПЭЈЕРЕФЫйТЪДг2.5GT/sжБНгЬсЩ§жС5GT/sЃЌЪЙЕЅЭЈЕРДјПэдіМгЕНСЫ500MB/sЃЌдкx16ХфжУЯТЃЌзмЭЬЭТСПДяЕНСЫСюШЫжѕФПЕФ8 GB/sЁЃPCIe 2.0БъзМдкММЪѕВуУцбгајСЫДЎааСДТЗМмЙЙЃЌЭЈЙ§гХЛЏаХКХЭъећадЩшМЦЃЌР§ШчдіЧПЗЂЩфЖЫдЄМгжиММЪѕЃЌВЛНіБЃГжСЫгыЧАДњЩшБИЕФЭъШЋЯђКѓМцШнадЃЌЛЙТњзуСЫИпЧхЯдПЈКЭИпЫйДцДЂЩшБИЕШЭтЩшЖдДјПэдіГЄЕФашЧѓЁЃетвЛАцБОЕФЙуЗКЦеМАЃЌМЋДѓЕиЭЦЖЏСЫЯћЗбЕчзгКЭЗўЮёЦїСьгђгВМўЕФЩ§МЖЛЛДњЃЌГЩЮЊPCIeММЪѕДгЦ№ВННзЖЮТѕЯђГЩЪьЦкЕФживЊРяГЬБЎЁЃ

PCle 3.0:CTLEММЪѕЮЊИпадФмЯдПЈгыSSDЦЬТЗ

дк2010Фъ11дТЃЌОЙ§ЖрДЮбгЦкЃЌPCIe 3.0БъзМжегке§ЪНЗЂВМЃЌБъжОзХPCIeММЪѕдкИпаЇДЋЪфЗНУцТѕГіСЫживЊЕФвЛВНЁЃетвЛАцБОЕФPCIeЪЕЯжСЫУПЭЈЕР8GT/sЕФДЋЪфЫйЖШЃЌЪЙЕЅЭЈЕРДјПэдіМгЕНДѓдМ1GB/sЃЌВЂПЊЪМВЩгУИќИпаЇЕФ128b/130bБрТыЗНАИЃЌвдНјвЛВНгХЛЏЪ§ОнДЋЪфаЇТЪЁЃЭЌЪБЃЌЫќБЃГжСЫгыPCIe 2.0дкШэМўКЭЛњаЕНгПкЗНУцЕФЭъШЋМцШнадЁЃ

ЮЊСЫгІЖдИпЦЕДЋЪфЕФашЧѓЃЌPCIe 3.0в§ШыСЫЯШНјЕФаХКХДІРэММЪѕЃЌШчНгЪеЖЫЕФСЌајЪБМфЯпадОљКтЃЈCTLEЃЉЃЌВЂНсКЯЗЂЫЭЦїЕФШЅМгжиЛњжЦКЭНгЪеЦїЕФОљКтЩшМЦЃЌгааЇВЙГЅСЫИпЦЕаХКХЕФЫЅМѕЃЌДгЖјЯджјЬсИпСЫаХКХЕФЭъећадЁЃДЫЭтЃЌЭЈЙ§авщеЛЕФгХЛЏЃЌPCIe 3.0НЕЕЭСЫДЋЪфбгГйЃЌВЂЩ§МЖСЫЕчдДЙмРэЛњжЦЃЌЪЕЯжСЫИќОЋЯИЕФЙІКФПижЦЃЌФмЙЛЭЌЪБТњзувЦЖЏЩшБИКЭЪ§ОнжааФЖдФмаЇЕФашЧѓЁЃдк2010ФъДњЃЌPCIe 3.0ГЩЮЊСЫЯћЗбМЖКЭЦѓвЕМЖгВМўЕФжїСїЛЅСЊБъзМЃЌЮЊИпадФмЯдПЈЁЂЙЬЬЌгВХЬЃЈSSDЃЉЕШЩшБИЬсЙЉСЫГфзуЕФДјПэжЇГжЃЌЭЦЖЏСЫМЦЫуЦНЬЈећЬхадФмЕФЯджјЬсЩ§ЁЃ

PCIe 4.0ЃКНтЫјNVMe SSDТњЫйЧБФмЃЌЭЦЖЏЯћЗбМЖЪаГЁЦеМА

2017ФъЃЌPCIe 4.0БъзМЗЂВМЃЌДЋЪфЫйТЪдйДЮЗБЖЃЌУПЭЈЕРЫйТЪДя16GT/sЃЌЕЅЭЈЕРДјПэдМ2GB/sЃЌБрТыЗНАИбигУ128b/130bИёЪНЁЃЭЈЙ§гХЛЏаХКХЭъећадЁЂдіЧПОљКтЫуЗЈгыЪБжгЭЌВНЛњжЦЃЌбгГЄСЫЭЈЕРЗЖЮЇЃЌЬсЩ§СЫГЄОрРыаХКХДЋЪфЕФЮШЖЈадЃЌШЗБЃСЫИпЫйТЪЯТСДТЗЕФПЩППадЁЃзїЮЊЪзИіШЋУцжЇГжNVMe SSDТњЫйдЫааЕФPCIeАцБОЃЌPCIe 4.0ЯджјЬсЩ§СЫДцДЂадФмЃЌТњзуСЫИпадФмМЦЫуКЭЪ§ОнжааФAIМгЫйЕШИпДјПэашЧѓГЁОАЁЃИУБъзМгЩAMDШёСњ3000ЯЕСаCPUТЪЯШВЩгУЃЌгЩгкЭъШЋЯђКѓМцШнЧАДњЩшБИЃЌЪЕЯжСЫЦНЛЌЙ§ЖЩЃЌВЂбИЫйдкЯћЗбМЖКЭЦѓвЕМЖЪаГЁЦеМАЃЌГЩЮЊСЌНгSSDЁЂGPUЕШИпЫйЭтЩшЕФКЫаФБъзМЁЃ

PCIe 5.0ЃКШ§ДѓММЪѕИяаТЃЌКЫаФадФмГжајЬсЩ§

здPCIe 4.0ЭЦГіКѓЃЌММЪѕЕФЕќДњНкзрЯджјМгПьЃЌеЙЯжГіаавЕЖдгкИпаЇФмЪ§ОнДЋЪфЕФЦШЧаашЧѓЁЃ

PCI-SIGгк2019Фъ5дТе§ЪНЗЂВМPCIe 5.0ЙцЗЖЃЌетвЛаТЙцЗЖдкБЃГжгыЧАДњММЪѕЯђКѓМцШнЕФЛљДЁЩЯЃЌЪЕЯжСЫДЋЪфЫйТЪЕФЗБЖЬсЩ§ЃЌДяЕН32GT/sЃЌЕЅЭЈЕРДјПэЬсЩ§жСдМ4GB/sЃЌЭЈЙ§x16ХфжУПЩЪЕЯж128GB/sЕФЭЬЭТСПЁЃетвЛОоДѓЕФДјПэЬсЩ§ЃЌзувджЇГХЪ§ОнжааФ400GEЭјТчЕФИпЫйДЋЪфашЧѓЃЌМЋДѓЕиТњзуСЫИпадФмМЦЫуЁЂДѓЪ§ОнЗжЮівдМАШЫЙЄжЧФмЕШСьгђЕФЦШЧаашвЊЁЃ

зїЮЊPCIe 4.0ЕФРЉеЙадЩ§МЖЃЌPCIe 5.0бгајСЫГЩЪьЕФММЪѕПђМмЃЌВЩгУгыЧАДњЯрЭЌЕФTx/RxВтЪдЗНЗЈМАЛљгкЁАблОІЁБПэЖШКЭИпЖШЕФНгЪеЦїгІСІЖЖЖЏаЃзМЛњжЦЁЃетжжбгајадЕФЩшМЦВЛНіНЕЕЭСЫММЪѕЧЈвЦЕФГЩБОКЭЗчЯеЃЌЛЙШЗБЃСЫаТРЯЩшБИЕФЮоЗьЖдНгЁЃНіЭЈЙ§еыЖдадЕФЕчЦјгХЛЏЃЌPCIe 5.0ЪЕЯжСЫадФмЕФдОЩ§ЃЌЪЙЕУЪ§ОнДЋЪфИќМгПьЫйКЭЮШЖЈЁЃ

PCIe 5.0ЕФКЫаФММЪѕИяаТЬхЯждкШ§ИіЗНУцЃК

• аТдіОљКтЕФДЋЪфавщЃКЭЈЙ§гХЛЏЪ§ОнДЋЪфЕФОљКтадЃЌШЗБЃИїЭЈЕРЕФРћгУаЇТЪзюДѓЛЏЃЌМѕЩйДЋЪфЦПОБЁЃ

• в§ШыИќЯШНјЕФДэЮѓМьВтКЭОРе§ЛњжЦЃКЬсЩ§СЫЪ§ОнДЋЪфЕФПЩППадЃЌгШЦфдкИпЫйДЋЪфЙ§ГЬжагааЇНЕЕЭСЫЮѓТыТЪЁЃ

• діЧПСЫЕчдДЙмРэЙІФмЃКЪЙЕУЩшБИдкБЃГжИпадФмЕФЭЌЪБЃЌФмЙЛИќМгжЧФмЕиЙмРэЕчдДЯћКФЃЌбгГЄЩшБИЪЙгУЪйУќВЂНЕЕЭдЫгЊГЩБОЁЃ

PCIe 5.0ЕФЭЦГіЃЌВЛНіЪЧММЪѕЩЯЕФНјВНЃЌвВЪЧЖдЮДРДЪ§ОнжааФЁЂдЦМЦЫуКЭБпдЕМЦЫуЛљДЁЩшЪЉЕФживЊжЇГжЁЃ

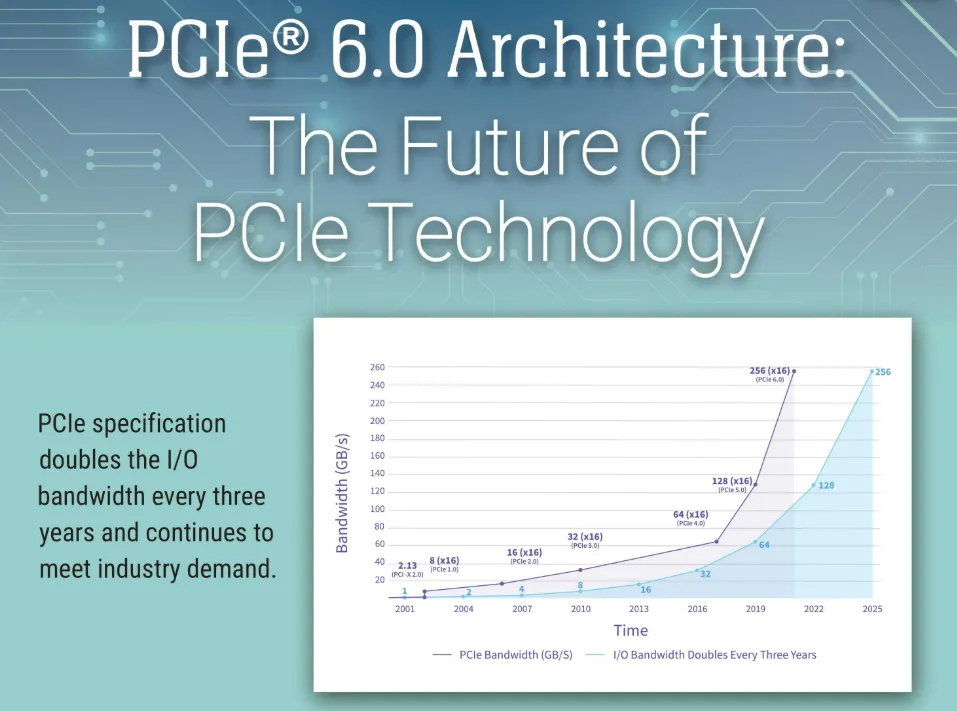

PCIe 6.0ЃКжиаТЖЈвхЪ§ОнДЋЪфаЇТЪБпНч

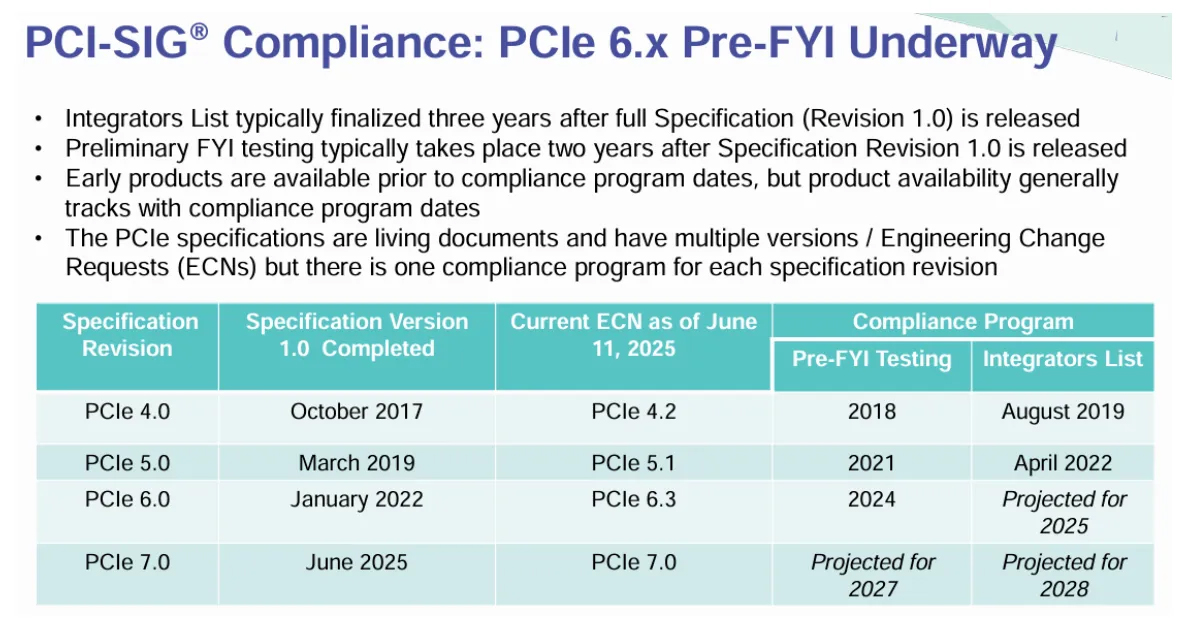

2022Фъ1дТЃЌPCI-SIGе§ЪНЗЂВМСЫPCIe 6.0ЙцЗЖЃЌетвЛЪТМўЮовЩБъжОзХИпЫйЛЅСЊММЪѕВНШыСЫвЛИіШЋаТЕФЗЂеЙНзЖЮЁЃPCIe 6.0зїЮЊИУММЪѕбнНјРњГЬжаЕФРяГЬБЎЪНЕФАцБОЃЌЪзДЮв§ШыСЫТіГхЗљЖШЕїжЦЃЈPAM4ЃЉаХКХБрТыММЪѕЁЃдкБЃГжаХЕРДјПэВЛБфЕФЧАЬсЯТЃЌЫќЪЕЯжСЫДЋЪфЫйТЪЕФЗБЖдіГЄЃЌНЋЕЅЭЈЕРЪ§ОнЫйТЪЬсЩ§жС64GT/sЃЌетвтЮЖзХЕЅЭЈЕРДјПэПЩвдДяЕН8GB/sЁЃЭЈЙ§x16ХфжУЃЌPCIe 6.0ФмЙЛЬсЙЉИпДя256GB/sЕФзмЭЬЭТСПЃЌетбљЕФадФмБэЯжЭъШЋФмЙЛТњзуЪ§ОнжааФ800GEЭјТчЕФИпЫйДЋЪфашЧѓЃЌДгЖјЮЊЪ§ОнДІРэКЭДЋЪфаЇТЪЕФЬсЩ§ЕьЖЈСЫМсЪЕЕФЛљДЁЁЃ

PCIe 6.0ЕФММЪѕИяаТАќРЈЮяРэВуЕФPAM4ЕїжЦЬцДњNRZБрТыЃЌЪЕЯжДјПэЗБЖЃЌВЂв§ШыЧАЯђОРДэЃЈFECЃЉВЙГЅаХКХЫ№КФЃЛТпМВугУ256BДЋЪфЕЅдЊЬцДњ128B/130BБрТыЃЌЬсЩ§ДЋЪфаЇТЪЃЛМцШнадгыПЩППадЗНУцЃЌбгајЯђКѓМцШнЩшМЦЃЌЭЈЙ§RetimerаХКХжиЙЙЕШММЪѕгХЛЏЃЌНЕЕЭбгГйЁЃЦфИпДјПэЪЪКЯAIбЕСЗЁЂдЦМЦЫуЕШГЁОАЃЌЙЎЙЬСЫдкМЦЫуЛњЯЕЭГЛЅСЊжаЕФКЫаФЕиЮЛЁЃ

PCIe 7.0ЃКЭЈЙ§ЙтбЇжиЖЈЪБЦїЭЛЦЦДЋЪфЯожЦ

2024ФъЃЌPCI-SIGзщжЏвбОЙЋВМСЫPCIe 7.0БъзМЁЃ зїЮЊзюаТАцБОЕФPCIeБъзМЃЌPCIe 7.0дкадФмЩЯЪЕЯжСЫгжвЛДЮЗЩдОЁЃдкPCIe 6.0ЕФЛљДЁЩЯЃЌPCIe 7.0НЋДјПэЗСЫвЛБЖЃЌУПЭЈЕРЕФДЋЪфЫйТЪЬсЩ§жС128GT/sЁЃЖдгкx16ЭЈЕРЃЌЦфЫЋЯђДјПэПЩДя512GB/sЃЌЖјЕЅЭЈЕРДјПэвВДяЕНСЫдМ16GB/sЁЃетбљЕФадФмЬсЩ§ЃЌНјвЛВНТњзуСЫЪ§ОнжааФКЭAIгІгУЖдМЋжТадФмЕФЦШЧаашЧѓЁЃ

дкММЪѕВуУцЃЌPCIe 7.0бгајСЫPCIe 6.0ЫљВЩгУЕФPAM4ЕїжЦММЪѕвдМАдкFLITФЃЪНЯТЕФ1b/1bБрТыЗНАИЃЌВЂЧвБЃСєСЫгыдчЦкАцБОЕФЯђЯТМцШнадЁЃИљОнPCI-SIGЕФЙцЛЎЃЌетвЛБъзМдкВнАИНзЖЮНЋзХжигкгХЛЏаХЕРВЮЪ§КЭЬсЩ§ФмаЇЫЎЦНЁЃе§БОЙцЗЖдЄМЦдк2025ФъЭъГЩжЦЖЈЃЌЫцКѓдк2027ФъНјаадЄЗЂВМВтЪдЃЈPre-FYIЃЉЁЃ

жЕЕУзЂвтЕФЪЧЃЌPCIe 7.0дЄМЦНЋв§ШыЙтбЇСЌНгЗНАИЃЌвдЬсЩ§ГЄОрРыДЋЪфЕФадФмЁЃВЛЙ§ЃЌвЕНчЦеБщШЯЮЊЦфШЋУцЦеМАПЩФмвЊЕШЕН2028ФъзѓгвЁЃетвЛжиДѓЩ§МЖНЋЮЊИпЫйЛЅСЊММЪѕДјРДаТЕФЗЂеЙЖЏСІЃЌГжајТњзуЪ§ОнУмМЏаЭгІгУГЁОАЕФашЧѓЁЃ

PCIe 8.0ЃКМЬајбгајДјПэЗБЖДЋЭГ

2025Фъ8дТЃЌPCI-SIGаЛсаћВМЃЌЫћУЧе§дкбаЗЂЕФPCIe 8.0ЙцЗЖНЋЪЙЪ§ОнЫйТЪЬсЩ§ЕН256GT/sЃЌЯрБШPCIe 7.0дйДЮЪЕЯжЫйЖШЗБЖЃЌВЂдЄМЦдк2028ФъЯђЛсдБЗЂВМИУЙцЗЖЁЃЭЈЙ§x16ЭЈЕРХфжУЃЌPCIe 8.0НЋЪЕЯжЫЋЯђДјПэ1TB/sЃЌЮЊашвЊИпДјПэЕФМЦЫуГЁОАЬсЙЉСЫЧАЫљЮДгаЕФадФмЬсЩ§ПеМфЁЃ

ИљОнPCI-SIGЕФЯъЯИЫЕУїЃЌPCIe 8.0ЙцЗЖВЛНідкадФмЗНУцЪЕЯжСЫДѓЗљЬсЩ§ЃЌЛЙНЋМЬајЮЌГжЯђКѓМцШнадЃЌЭЌЪБТњзуЕЭбгГйЁЂИпПЩППадвдМАЙІКФгХЛЏЕФЩшМЦФПБъЁЃЦфжаЃЌЙиМќЬиадАќРЈЃК

• дЪМБШЬиТЪЬсЩ§жС256.0 GT/sЃЌдкx16ХфжУЯТЃЌЪЕЯжСюШЫОЊЬОЕФ1 TB/sЫЋЯђДЋЪфЫйТЪЁЃ

• в§ШыШЋаТЕФСЌНгЦїММЪѕЃЌвдгІЖдИќИпБъзМЕФаХКХЭъећадашЧѓЁЃ

• ЭЈЙ§гХЛЏбгГйКЭЧАЯђОРДэЃЈFECЃЉЛњжЦЃЌШЗБЃЪ§ОнДЋЪфЕФИпЖШПЩППадЁЃ

• діЧПавщЙІФмЃЌЯджјЬсЩ§гааЇДјПэЕФРћгУТЪЁЃ

• ГжајНЕЕЭЙІКФЃЌвдЪЪгІТЬЩЋЪ§ОнжааФКЭвЦЖЏМЦЫуЩшБИЕФашЧѓЁЃ

вРОнPCI-SIGЙЋВМЕФЫйТЪЗЂеЙЧїЪЦПЩвдПДГіЃЌPCIeБъзМДѓдМУПШ§ЕНЫФФъБуЛсЭъГЩвЛДЮЫйЖШЕФЗБЖЕќДњЁЃдкДгPCIe 7.0Яђ8.0ЕФЗЩдОжаЃЌЭЈЕРаХКХжЪСПЁЂзпЯпЩшМЦвдМАЗтзАВФСЯЖМНЋУцСйШЋаТЕФЬєеНЁЃ

еЙЭћЮДРДЃЌPCIe 8.0ПЩФмЛсв§СьвдЯТММЪѕЕФЗЂеЙЗНЯђЃК

• ЯШНјЗтзАгыаОЦЌМфЛЅСЌЃКаЭЌЩшМЦНЋГЩЮЊЙЙНЈИпадФмМЦЫуЦНЬЈЕФКЫаФОКељСІЫљдкЁЃ

• ЙтЛЅСЌММЪѕЃКЫцзХДЋЪфЫйТЪЕФВЛЖЯЬсЩ§ЃЌЕчаХКХЭъећадж№НЅЪмЯоЃЌЙтЛЅСЌММЪѕгаЭћдкPCIe 9.0ЩѕжСИќдчЕФРЉеЙжаБЛв§ШыЁЃ

• ЯЕЭГЙІКФгХЛЏЃКЪ§ОнжааФЖдФмаЇЕФбЯПСвЊЧѓЃЌНЋГжајЭЦЖЏPCIeавщдкЕЭЙІКФЬиадЗНУцЕФЕќДњЩ§МЖЁЃ

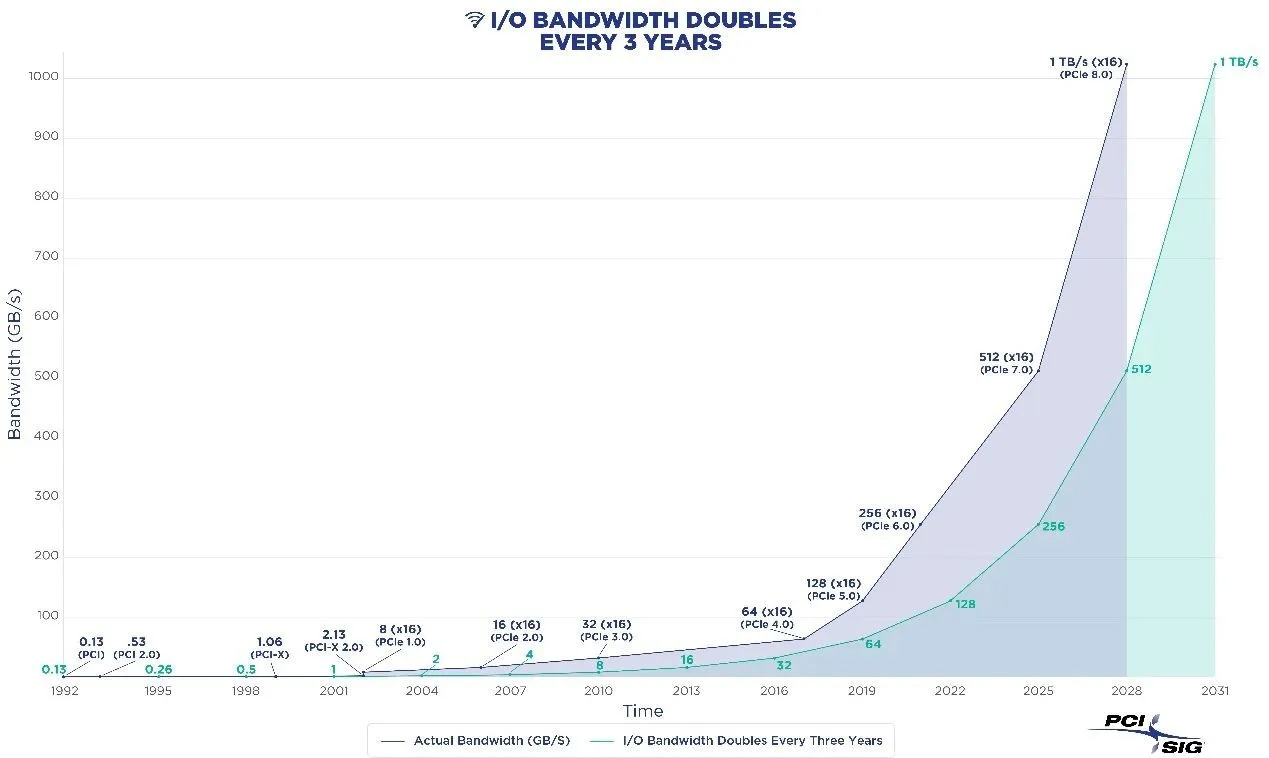

PCIeММЪѕЙ§ШЅЖўЪЎЖрФъвЛжБЪЧИпадФмЁЂЕЭбгГйI/OСЌНгЕФЪзбЁЁЃДг1.0ЕН8.0ЃЌУПвЛДњЫйТЪМИКѕЗБЖЃЌЯдЪОГіЦфбИУЭЕФЗЂеЙЫйЖШЁЃетБГКѓЪЧМЦЫуашЧѓЕФБЌЗЂЃЌЗДгГГіPCIeЖдИпадФмМЦЫуКЭЪ§ОнДЋЪфЕФжЇГХзїгУЁЃ

AI/MLбЕСЗгыЭЦРэашЧѓЫцзХДѓФЃаЭВЮЪ§ЕФдіМгЖјМЄдіЁЃИпЫйЭјТчгыБпдЕМЦЫувЊЧѓЕЭбгГйКЭИпДјПэЁЃСПзгМЦЫугыHPCашвЊИпЭЬЭТЁЂЕЭбгГйЕФЛЅСЌМмЙЙЁЃЦћГЕгыЙњЗРСьгђЖдЪЕЪБадКЭПЩППадгаИпвЊЧѓЃЌЪЙИпЫйзмЯпБъзМГЩЮЊЙиМќЁЃ

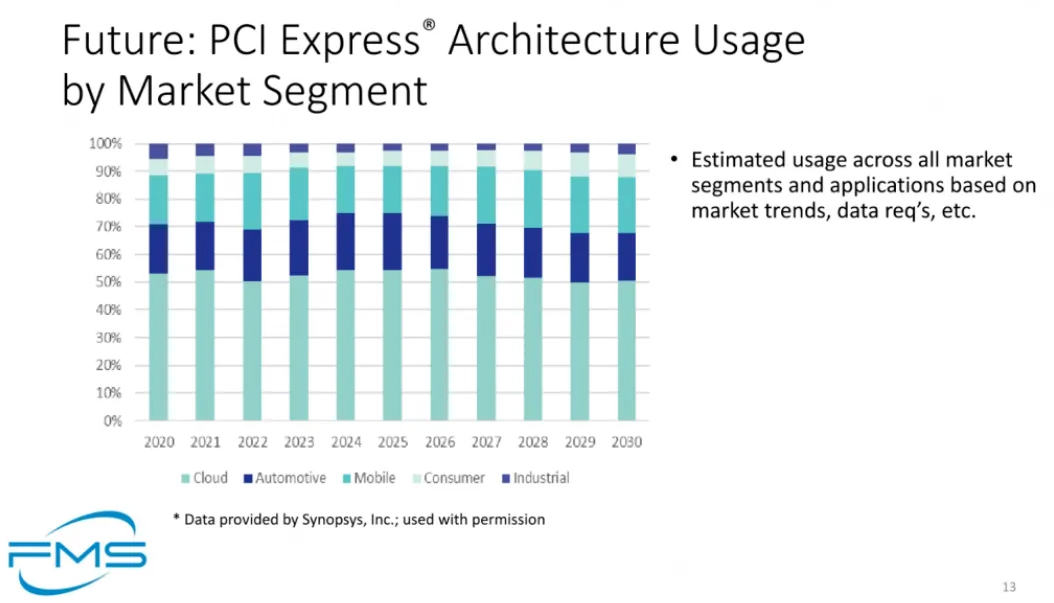

дкгІгУЪаГЁЗНУцЃЌдЦМЦЫуСьгђеМОнPCIeзюДѓЗнЖюЃЌдЄМЦНЋГжајжїЕМЪ§ОнжааФКЭЗўЮёЦїЪаГЁЁЃЦћГЕЪаГЁгЩгкAIКЭADASашЧѓдіГЄЃЌPCIeВЩгУТЪЮШВНЩЯЩ§ЁЃвЦЖЏЩшБИЪаГЁЮШЖЈдк10%-20%ЃЌжївЊгУгкжЧФмЩшБИЁЃЯћЗбРрЕчзгЪаГЁж№ВНРЉДѓЃЌдкМвЭЅЩшБИКЭИіШЫЕчФджагІгУЁЃЙЄвЕСьгђЫцзХздЖЏЛЏКЭIoTЗЂеЙЃЌPCIeВЩгУТЪЛКТ§діГЄЃЌживЊадШевцЭЙЯдЁЃ

ОпЬхЖјбдЃЌPCIeНгПкЦОНшЦфзПдНЕФИпДјПэгыЕЭбгГйЬиадЃЌдкжкЖрМЦЫуЩшБИжаЕУЕНСЫЙуЗКгІгУЃЌАќРЈЃК

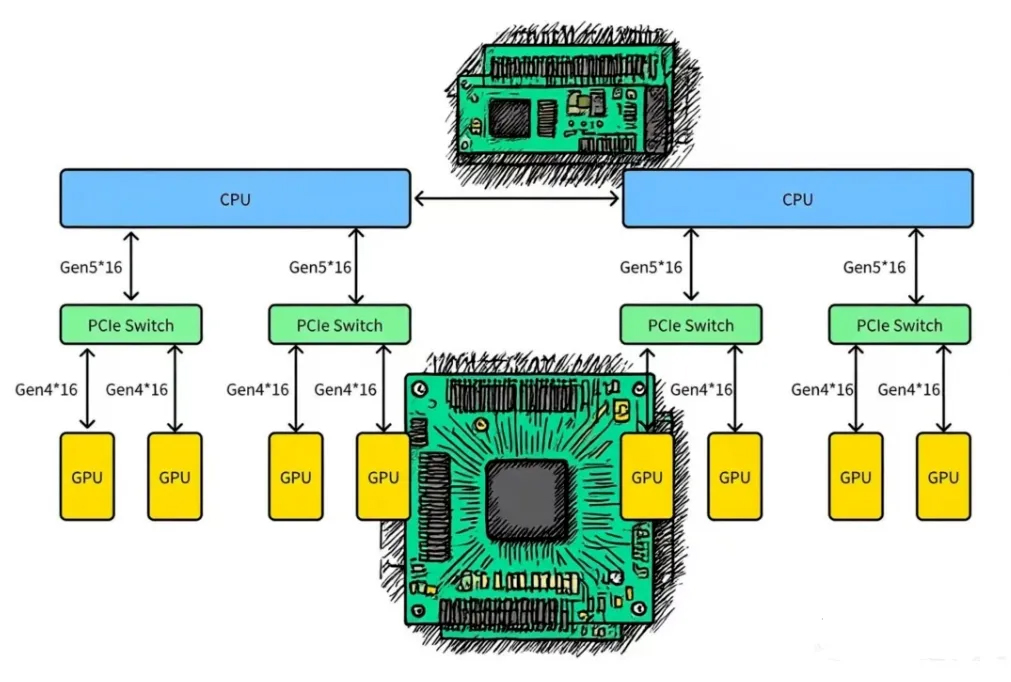

• ЭМаЮДІРэЦїЃЈGPUЃЉЃКPCIeНгПкБЛгУгкСЌНгИпадФмGPUЃЌЮЊЭМаЮфжШОвдМАШЫЙЄжЧФмбЕСЗЕШЗБжиЕФШЮЮёЬсЙЉСЫИпЫйЪ§ОнДЋЪфЕФЭЈЕРЃЌДѓЗљЬсЩ§СЫДІРэаЇТЪЁЃ

• CPUгыжїАхаОЦЌзщЭЈаХЃКCPUЭЈЙ§PCIeЭЈЕРгыжїАхФЯЧХаОЦЌЃЈPCHЃЉЪЕЯжЭЈаХЃЌДгЖјгааЇПижЦжмБпЩшБИЃЌР§ШчUSBКЭSATAНгПкЃЌШЗБЃЯЕЭГдЫааЕФЫГГЉгыИпаЇЁЃ

• ЙЬЬЌгВХЬЃЈSSDЃЉЃКPCIeНгПкдкNVMe SSDжаБЛЙуЗКгІгУЃЌЯджјЬсЩ§СЫДцДЂЩшБИЕФЖСаДЫйЖШЃЌЫѕЖЬСЫЪ§ОнЗУЮЪЕФЕШД§ЪБМфЁЃ

• ЭјТчНгПкПЈЃЈNICЃЉЃКИпДјПэЕФЭјТчНгПкПЈЭЈГЃВЩгУPCIeНгПкЃЌвдШЗБЃЪ§ОнДЋЪфЕФИпаЇадЃЌТњзуШевцдіГЄЕФЭјТчашЧѓЁЃ

• ИпадФмМЦЫуЃЈHPCЃЉЃКдкHPCЯЕЭГжаЃЌPCIeНгПкгУгкСЌНгВЛЭЌЕФМЦЫуНкЕуКЭДцДЂЩшБИЃЌЪЕЯжСЫЪ§ОнЕФИпЫйДЋЪфЃЌжњСІПЦбЇбаОПКЭИДдгМЦЫуЁЃ

ЯдЖјвзМћЃЌPCIeзїЮЊвЛжжБЛЙуЗКВЩгУЕФаОЦЌМфЛЅСЊавщЃЌЦфМмЙЙгХЪЦЯджјМѕЩйСЫЛЅВйзїадЗНУцЕФЬєеНЁЃетвЛЬиадМЋДѓЕиДйНјСЫвьЙЙМЦЫуЕФЗЂеЙЃЌМДНЋCPUЁЂGPUКЭAIМгЫйЦїНјаагаЛњНсКЯЃЌЭЈЙ§БъзМЛЏЕФЛЅСЊММЪѕЃЌМЋДѓЕиЬсЩ§СЫвьЙЙМЦЫуЕФаЇТЪКЭадФмЁЃ

ЬиБ№ЪЧдкЖдAIММЪѕЕФжЇГжЗНУцЃЌPCIeОпгаИпДјПэЁЂЕЭбгГйКЭСМКУМцШнадЕФЬиЕуЃЌЪЙЦфГЩЮЊжЇГжAIММЪѕЙуЗКВПЪ№КЭдіГЄЕФживЊЛљЪЏЁЃЦфГіЩЋЕФЧАЯђКЭКѓЯђМцШнадАяжњОіВпепдкВПЪ№AIММЪѕЪБгЕгаИќИпЕФСщЛюадЃЌФмЙЛгааЇЫѕЖЬВПЪ№жмЦкЃЌВЂНЕЕЭВПЪ№ЗчЯеЃЌетвВе§ЪЧPCIeдкAIаавЕжаЕУЕНИпЖШВЩгУЕФдвђЁЃ

ЛљгкДЫЃЌЯрЙиЪ§ОндЄВтЃЌЕН2030ФъЃЌPCIeММЪѕдкAIЪаГЁЃЈКИЧБпдЕAIКЭЪ§ОнжааФAIЃЉЕФзмПЩгУЪаГЁдЄМЦПЩДя27.84вкУРдЊЃЌФъОљИДКЯдіГЄТЪДяЕН22%ЁЃЦфжаЃЌБпдЕAIЪаГЁдЄМЦНЋвд50%ЕФФъОљИДКЯдіГЄТЪПьЫйдіГЄЃЌетжївЊЕУвцгкЦѓвЕВЛЖЯВПЪ№БпдЕЗўЮёЦївдМАAIММЪѕЕФШевцЦеМАЃЌетЮовЩНЋНјвЛВНЭЦЖЏPCIeММЪѕЕФЗЂеЙгыгІгУЁЃ