芯片要 “换玩法” 了?关键是 Chiplet

1965年,英特尔公司的联合创始人戈登・摩尔提出了著名的“摩尔定律”。这一具有前瞻性的观察,在过去半个多世纪里,极大地推动了集成电路(IC)性能的持续提升和成本的显著下降,进而成为现代数字技术迅猛发展的基石。摩尔定律的核心内容为:大约每两年,半导体芯片上的晶体管数量便会翻一倍。然而,随着时间的推移,这一规律正面临着前所未有的挑战。

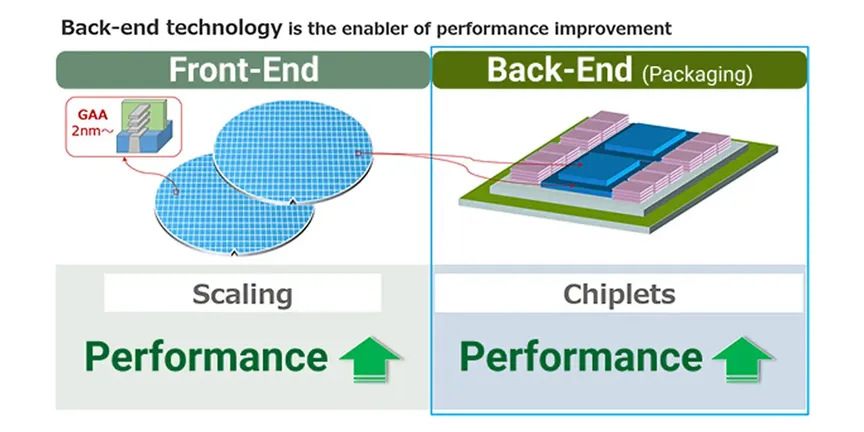

近年来,芯片电路尺寸的微型化进程逐渐放缓,当前的线宽已精确至仅几纳米的程度。工程师们在技术研发中遭遇了诸多难题,包括但不限于物理极限的逼近、制造工艺的日益复杂,以及成本压力的不断攀升。电路尺寸的进一步缩小不仅导致生产良率下降,使得大规模生产出高质量芯片的难度加大,还对半导体制造工厂的建设与运营提出了更高的资金和技术要求。因此,业内许多人开始认为,摩尔定律的持续有效性正受到严峻考验,其对技术进步的指导作用或许即将走到尽头。

摩尔定律的终结带来了一项新的进步:芯粒。

芯粒(Chiplet)是指执行特定功能的芯片(裸片)的一小部分,原本是单个大芯片的一部分。通过芯粒集成,多个芯粒可以组合成一个封装,组成一个完整的系统。这一技术的出现,为半导体行业带来了革命性的变革。过去,所有芯片功能都必须构建在单个晶圆上。这种方式不仅在技术实现上存在诸多挑战,而且一旦芯片的一部分出现缺陷,整个芯片也必须丢弃,造成了巨大的资源浪费。但有了芯粒技术后,情况发生了根本性的改变。我们现在只使用“良好芯片”(即“已知良好芯片”(KGD)),这极大地提高了制造良率和效率。芯粒技术通过将大芯片分解为多个小芯片,再进行独立制造和测试,最后组合封装,使得每一部分都可以得到充分的优化和利用。这种模块化的方法不仅降低了制造成本,还缩短了产品上市的时间,为芯片设计的灵活性和创新性提供了更大的空间。

异构集成是一项先进的封装技术,它能够将使用不同制造工艺、具有各异功能的芯片整合到一个单一的封装之中。这种技术在小芯粒领域表现尤为出色,它能够有效地混合和匹配各种不同类型的电路。例如,对于高性能的计算组件,可采用最为尖端的半导体工艺来制造;而存储器和模拟部件,则可运用更传统且成本效益更高的技术进行生产。这种平衡策略不仅控制了成本,还大幅提升了整体性能,因此备受汽车行业的青睐。

目前,一些大型汽车制造商已经开始利用这一技术开发面向未来汽车的片上系统(SoC),并计划在2030年后应用于大规模生产。Chiplet技术的核心优势在于其能够显著增强汽车半导体的性能与功能,尤其是在提升AI计算和图形处理能力方面效果显著,同时,还能够提高芯片的产量。

一些汽车部件必须具备高度可靠的安全性,这些被称为功能安全部件的芯片,通常采用更成熟且经过时间检验的半导体技术制造。然而,现代系统如高级驾驶辅助系统(ADAS)和软件定义汽车(SDV)则需要性能更为强大的芯片,而这正是小芯粒技术大显身手的领域。通过将功能安全部件中的微型计算机、大容量内存与用于自动驾驶的AI处理器相结合,制造商能够根据不同汽车厂商的需求,快速定制专属的片上系统。

这些优势并不仅仅局限于汽车领域,Chiplet技术正在向人工智能和电信等行业拓展,成为推动众多行业创新的重要力量。这一技术正迅速普及,有望成为未来半导体行业的核心技术。

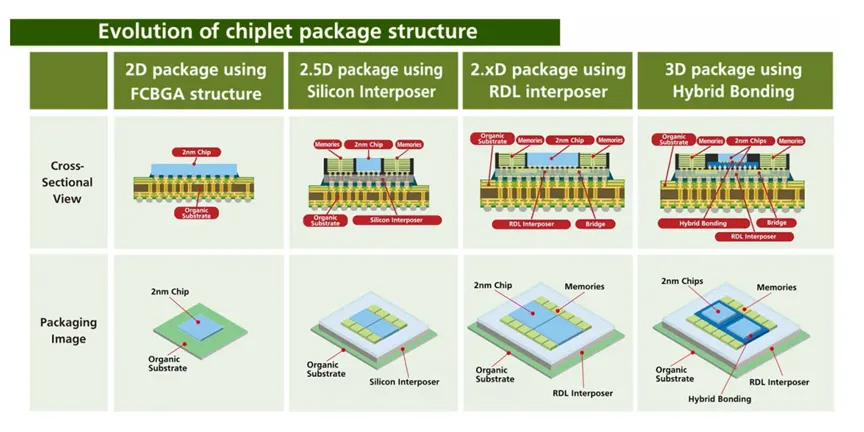

芯粒技术的实现依赖于一种能够在紧凑的空间内高速连接多个芯片的技术。中介层是这一过程的关键组成部分,通常由硅材料制成,位于芯片的下方。它就像一块电路板,将各个芯片连接起来,帮助它们实现相互通信。中介层的性能越好,芯片之间的连接就越紧密,电信号的交换速度也越快。

在高效供电方面,先进的芯粒集成技术也发挥着举足轻重的作用。通过在芯片之间添加大量微小的金属连接点,即便在狭小的空间内,也能为电流和数据传输提供充足的路径。这不仅实现了高速的数据传输,还能够充分利用芯片封装中的有限空间。

目前,芯粒集成的主流方法是2.5D集成,即将多个芯片放入单个封装中。然而,下一个重大进展将是3D集成,这是一种将芯片垂直堆叠的技术。在2.5D结构中,芯片并排排列在中介层上,以实现高密度的连接。相比之下,3D集成则利用称为硅通孔(TSV)的技术将芯片垂直堆叠,从而实现更高的集成度。

通过将灵活的芯片设计(将不同功能和电路类型分离)与 3D 集成相结合,工程师可以构建更快、更小、更节能的半导体。这种方法将不同的芯片功能模块化和分层,使得各种电路类型可以独立优化和升级。将内存和处理单元直接堆叠在一起,可以实现对大量数据的高速访问,这对于快速执行人工智能和其他高性能流程非常有利。这种架构极大地缩短了数据访问的延迟时间,显著提高了计算效率。

另一方面,垂直堆叠芯片也带来了新的挑战。热量更容易积聚,因此热管理和保持高制造良率变得更加困难。堆叠的芯片层数越多,产生的热量就越集中,这可能导致芯片性能下降甚至失效。为了克服这些问题,世界各地的研究人员正在研究先进封装技术的新方法,以更好地应对热挑战。例如,采用新型散热材料、优化芯片布局以及设计更有效的散热通道等。

但这并没有减缓创新的步伐。芯粒与 3D 集成的结合如今被视为一项颠覆性的创新,它有可能取代摩尔定律,引领半导体发展的下一个时代。芯粒技术允许将不同功能的芯片模块(芯粒)组合在一起,形成一个完整的系统级芯片(SoC)。这种方法不仅提高了芯片的性能和集成度,还降低了设计和制造成本。通过 3D 集成,这些芯粒可以在垂直方向上堆叠,进一步减小芯片的面积和功耗,同时提高数据处理速度。

随着人工智能、物联网和 5G 通信等技术的快速发展,对高性能、低功耗半导体芯片的需求不断增长。芯粒和 3D 集成技术的结合有望满足这些需求,为未来的电子设备带来更强大的功能和更高的能效比。在不远的将来,我们可能会看到更多采用这种先进技术的电子产品问世,从而改变我们的生活方式和工作方式。